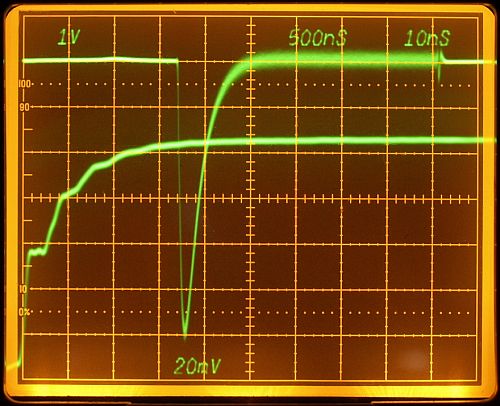

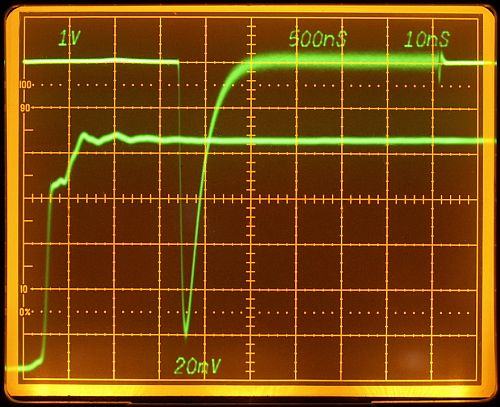

Time corrected input signal with a bad termination - slow extreme.

| Same conditions as decribes above, but with an increased series resistors of some hundred ohms. This takes high frequency contents away and decrease slew rate. Such a waveform is dangerous, because the rising edge is very distorted. In the worthwile midrange of the slope there is a small flat "shoulder" area, triggering in this area would cause increased jitter and a fast logic device could even start with oscillations or ringing. The good thing in this experiment, the waveform of the gated-settling-time has not changed. |

Potentiometer trimmed to 53 ohms, resulting in an undistorted rising slope (within 0V to 4V) - less overshooting - oscilloscope will trigger save.

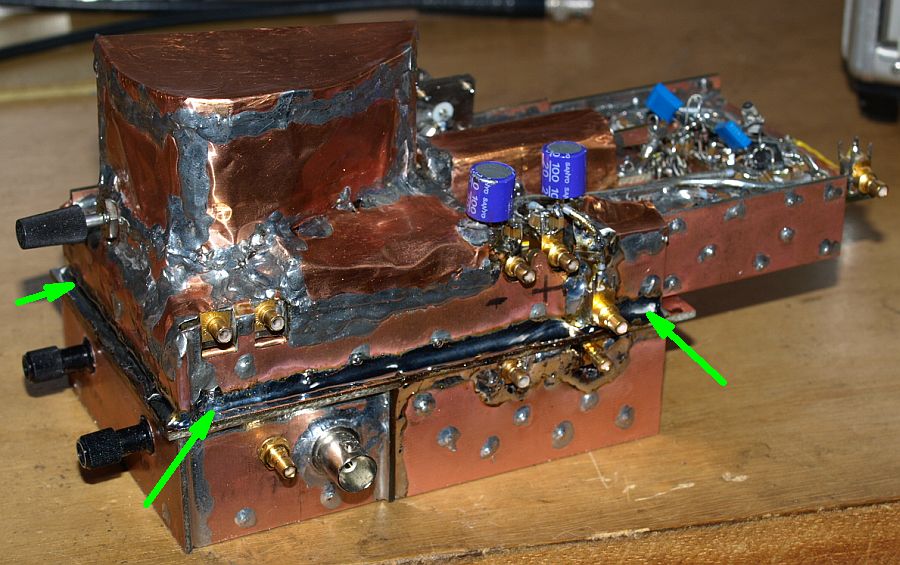

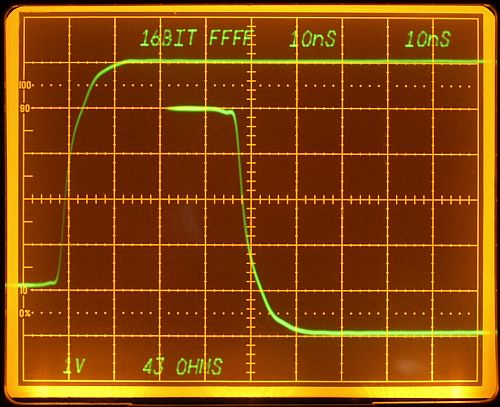

Digital Signals with Trimmed Termination

Photos always showing the rising and falling edge.

All measurements done with a 7904, 7A26, 7B85, 7B80 and a good quality 1:10 passive probe with a low inductance GND spring on the tip.

Time Corrected Input Signal - 53 ohms

(exception - using a 40 cm coax cable instead of the probe tip).

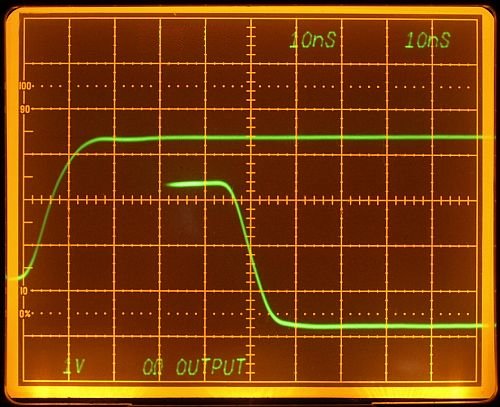

Window generator input, using a 88 ohms series resistor. Nice waveform - device will trigger save.

Window generator output, using a zero ohms series resistor. Nice waveform - diode bridge will switch save.

No series resistor was the best choice here.

The falling edge switch the HF transistors in the diode brigde.

Signal is steep, undistorted and fast.

Load DAC and all 16 Bit signals for FFFF full scale step - looks good.

43 ohms series resistor.